Introduction

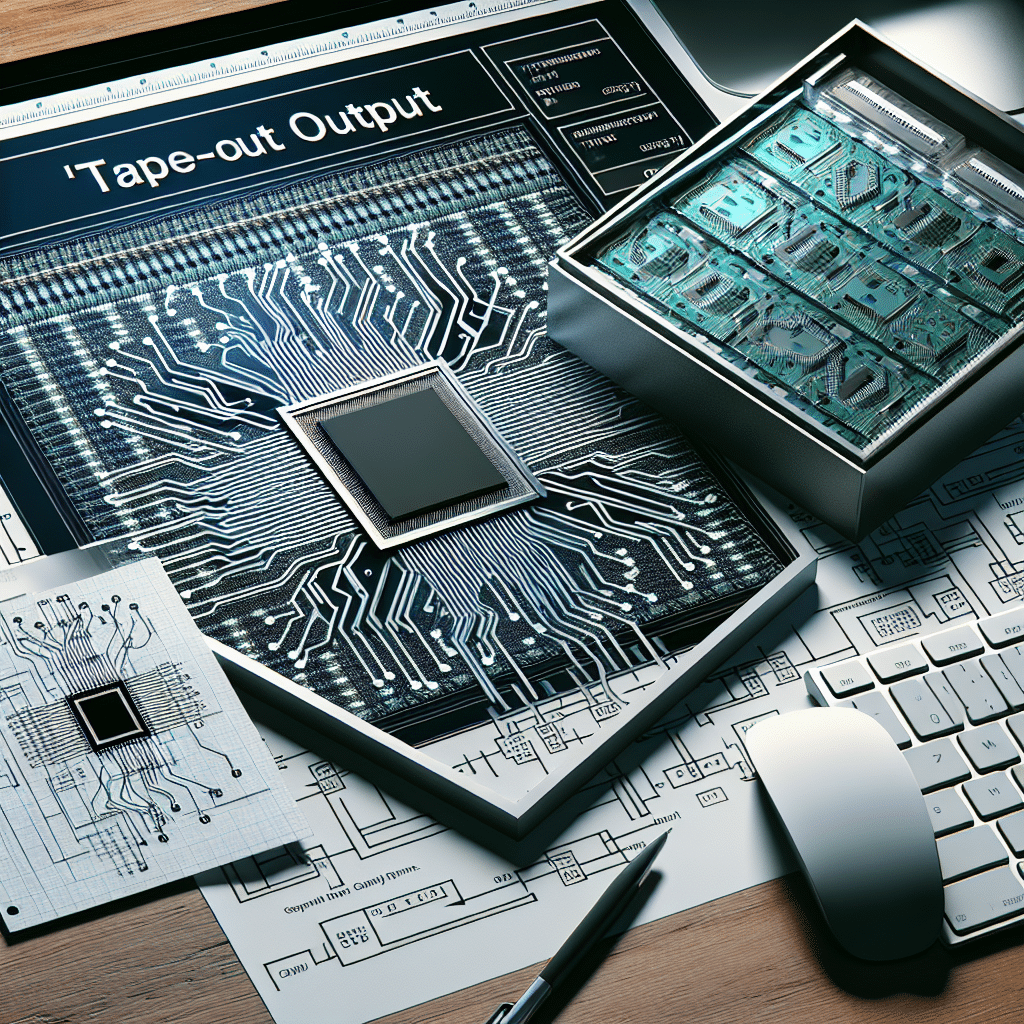

A tape out output refers to the final stage in the design process of integrated circuits (ICs), where the design data is prepared for manufacturing. It produces the layout files and specifications necessary for photolithography in semiconductor fabrication. Essentially, a tape out output symbolizes readiness to move from the design phase to actual production. It encompasses various technical components such as layout design, design rule checks (DRC), and electrical rule checks (ERC), ensuring that the integrated circuit meets all necessary specifications for functionality and manufacturability.

Understanding Tape Out Outputs: An Overview

At its core, the tape out process marks a significant milestone in chip design and production. Before addressing the specifics of tape out outputs, it is vital to understand the terms and processes leading up to it.

What is Tape Out?

Tape out is a term originating from the traditional method of storing design data on magnetic tape. In modern contexts, it refers to the completion of a chip’s design which is transitioned to a production-ready state. During this phase, all design data, layout, and schematics are finalized and verified.

Importance of Tape Out Outputs

This output is crucial as it ensures that the IC can be manufactured without unnecessary complications or errors. A comprehensive and accurate tape out output significantly reduces the chances of defects during manufacturing, thus safeguarding investment and timelines.

Components of a Tape Out Output

The tape out output consists of several components that are meticulously validated to ensure a successful transition to manufacturing. Here’s a breakdown of these components:

1. Layout Designs

Layout designs are the graphical representations of the silicon chip, detailing where various components such as transistors, resistors, and capacitors will be placed. High-precision software tools like Cadence and Synopsys are typically used to generate these layouts. They include layers that specify routing, power distribution, and cell layouts.

2. Design Rule Checks (DRC)

Design Rule Checks verify that the layout adheres to manufacturing constraints like spacing, width, and area. This step is crucial to prevent manufacturing defects that could arise from violating physical design rules set by manufacturers.

3. Electrical Rule Checks (ERC)

ERC ensures that the electrical characteristics of the design meet the specified criteria. It checks for potential issues like short circuits or incorrect pin assignments that could compromise the functionality of the IC.

4. GDSII Files

The GDSII file format is the standard for tape out outputs. It encodes the geometrical layout of the circuit in a way that is compatible with photolithography processes used in semiconductor fabrication. This format encapsulates all layers of design information necessary for chip production.

5. Verification Reports

After completing the checks, verification reports are generated. These reports document any discrepancies found and how they were addressed, ensuring a track record for future reference and troubleshooting.

Process of Tape Out

The tape out process can be intricate, often requiring several iterations to perfect the design. Here’s a stepwise breakdown of the process leading up to and including tape out:

1. Initial Design and Simulation

The design phase begins with schematic capture and simulation. Here, electronic design automation (EDA) tools simulate the behavior of the circuit according to its intended function.

2. Synthesis

Following validation through simulation, the logical design is synthesized into a gate-level representation. This is crucial for identifying how the design will be constructed using electronic components.

3. Place and Route

Once the synthesis is complete, the next step involves placing components within a predefined area and routing the connections between them. This step is key to ensuring an efficient layout that meets all design constraints.

4. Performing DRC and ERC

At this stage, both Design Rule Checks and Electrical Rule Checks are performed to confirm that the layout meets required standards and that all design criteria are satisfied.

5. Final Sign-Off

After ensuring the layout passes all necessary checks, the design is signed off by qualified engineers, marking the transition to the tape out output phase.

6. Generating the Tape Out Output

The final design files, including GDSII files, are generated and compiled. These files are then sent to the fabrication facility for manufacturing.

Challenges in Tape Out Process

While tape out represents the culmination of design endeavors, it is fraught with challenges that need to be addressed to ensure a smooth transition to production:

1. Complexity of Designs

As circuits become more complex, ensuring that all design rules are adhered to becomes increasingly challenging. This complexity often necessitates sophisticated EDA tools and expertise.

2. Debugging Incurred Errors

Errors identified during the verification stages can lead to extended timelines and increased costs. An agile approach to debugging is essential to mitigate this.

3. Communication Gaps

Effective communication is required among the design team, manufacturing team, and stakeholders. Gaps in communication can lead to misunderstandings that potentially delay the tape out process.

Future Trends in Tape Out Outputs

The semiconductor industry is rapidly evolving, and several trends are shaping the future of tape out processes and outputs:

1. Increased Automation

With advancements in AI and machine learning, automation in the design verification process is poised for growth. This will likely enhance accuracy and reduce time spent on DRC and ERC.

2. Improved EDA Tools

As EDA tools become more sophisticated, the ability to handle complex designs will improve, leading to smoother tape out processes. Enhanced simulation capabilities will also allow for more rigorous pre-tape out testing.

3. Green Manufacturing Practices

As sustainability becomes a key concern, future tape out processes are likely to incorporate green manufacturing practices, aiming to reduce waste and promote energy-efficient methods.

Frequently Asked Questions (FAQs)

What happens after tape out?

After tape out, the design files are sent to semiconductor manufacturing facilities, where the actual fabrication of the IC begins. This process includes steps like wafer fabrication, packaging, and testing.

How long does the tape out process take?

The duration of the tape out process can vary widely, typically taking anywhere from a few weeks to several months, depending on the complexity of the design and the efficiency of the design team.

What are common tools used in tape out?

Common tools include Cadence, Synopsys, and Mentor Graphics, which provide functionalities for layout design, DRC, ERC, and GDSII file generation.

What are the costs associated with tape out?

Costs can vary significantly based on design complexity, tool licensing fees, and manufacturing chosen processes. Budget planning is essential to avoid unexpected expenses.

Can tape out outputs be reversed?

Reversing a tape out output is generally not feasible, as it signifies a finalized design. However, revisions may be considered if discrepancies found during fabrication warrant changes, necessitating a new tape out.